초미세 반도체 공정 기술과 핀펫(FinFET) 트랜지스터 사용이 증가하면서, 온칩 인터커넥트는 타이밍 클로저 이슈의 주요 원인이다. 이는 대개 설계 공정의 후반부에 발견되기 때문에 개발 일정에 차질을 빚게 하거나 제품 출시를 지연시키곤 한다. 현재 설계팀들은 ECO(engineering change order) 공정을 통해 칩 넷리스트에 파이프라인 단을 수동으로 삽입해 문제를 처리하지만 쉽지 않은 일이다.

SoC(system-on-chip) 인터커넥트 IP 기업인 아테리스(Arteris, 지사장 연명흠)가 차세대 인터커넥트 타이밍 자동화 솔루션인 ‘PIANO 2.0 타이밍 클로저 패키지(Timing Closer Package)’를 발표했다.

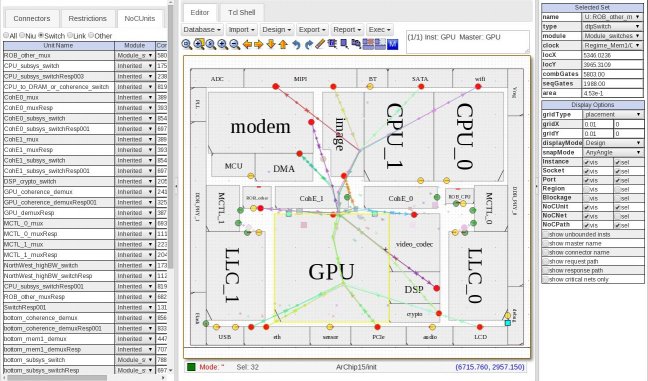

PIANO 2.0은 FlexNoC Physical 패키지 사용 고객들을 위해 캐시 코히어런트 및 비(非)코히어런트 서브시스템 모두에 자동화된 인터커넥트 타이밍 클로저를 제공한다. PIANO 2.0은 SoC 설계 플로우의 초반부터 작동하는 기술을 이용해 백엔드 타이밍 문제를 해결해 일정 지연의 위험을 줄여준다.

PIANO는 개별 인터커넥트 링크와 트레이스의 길이를 계산한 다음, 반도체 기술 공정에 대한 정보와 성능 목표를 활용하여 인터커넥트 파이프라인을 가까운 타이밍에 자동으로 연결한다. 그런 다음, PIANO는 시놉시스(Synopsis)나 케이던스(Cadence) 툴 체인의 물리적 합성 능력을 이용해 이 타이밍 클로저 회로에 대한 평가를 지원한다. PIANO 2.0 타이밍 클로저 패키지는 FlexNoC와 Ncore 인터커넥트 IP 라이선스에 추가하여 지금 즉시 활용이 가능하며, 추가적인 기능들은 2017년 2분기에 제공된다.

아테리스의 찰스 자낙(K. Charles Janac) 회장 겸 CEO는 “PIANO 2.0은 아테리스의 Ncore 캐시 코히어런트 인터커넥트와 FlexNoC 비-코히어런트 인터커넥트 IP 제품 모두와 동작하는 차세대 자동 인터커넥트 타이밍 클로저 솔루션을 공급하기 위해 업계 선도적인 반도체 설계팀들과 18개월 동안 협력한 결과물”이라고 말했다.

이향선기자 hslee@nextdaily.co.kr